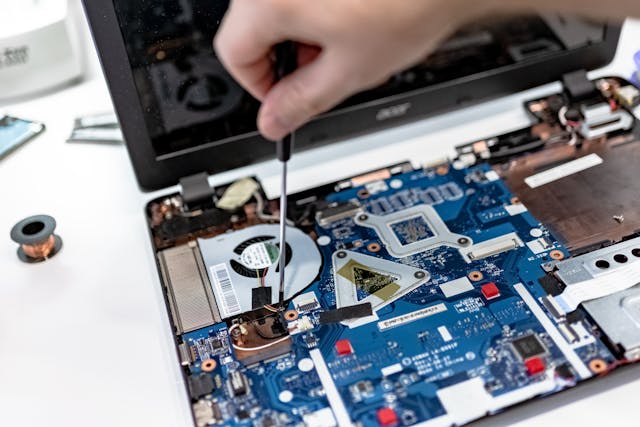

在低速电路中,走线更多被视为简单的连接导体;但当接口速率与信号频谱扩展至GHz范围,PCB走线的电气行为更接近传输线系统。此时,许多看似“逻辑正确”的设计仍可能在物理层出现异常,其中最常见的一类就是由阻抗不连续引发的信号反射。它可能带来眼图裕量下降与误码率上升,也可能在极端情况下触发器件输入保护结构承受过压应力,形成可靠性隐患。

阻抗不连续的本质:能量在边界处无法被“顺畅吸收”

理解反射现象,一个实用的类比是流体管路:管径连续时能量平稳传递;当出现突然变窄或变粗的结构变化,流体会在交界处产生回波与扰动。高速互连中的“管径变化”对应的就是特征阻抗的突变。对于单端常见的50Ω、差分常见的100Ω链路而言,任何结构或工艺偏差导致的阻抗偏离,都可能使部分能量反射回源端或在链路内来回叠加。

工程实践中,阻抗不连续往往来自以下几类位置:

- 过孔与换层结构:过孔寄生电容、残桩(stub)等会改变局部等效阻抗,形成反射源。

- 连接器与接口过渡:结构几何变化、引脚与回流路径不连续,容易形成局部不匹配。

- 线宽/间距变化:设计变更、布线约束或制造公差引起的几何突变,会直接带来阻抗漂移。

- 端接策略不当:源端/终端阻抗与传输线目标阻抗不一致,反射能量无法被有效吸收。

反射带来的三类典型后果:波形畸变不止“看着难看”

当反射能量叠加到原始信号上,时域波形会出现多种失真形态,影响不仅限于信号质量,也会触发可靠性与EMI风险:

1)过冲与下冲:电压越界带来的器件应力

反射叠加可能使电压瞬态超过逻辑电平上限(过冲)或低于下限(下冲)。过冲会对输入端保护结构产生额外应力,下冲则可能引发阈值附近的误触发与时序异常。

2)振铃:多次反射叠加后的高频振荡

当链路上存在多个不连续点,信号能量可能在源端与负载端之间反复往返,形成振铃。其直接影响是提高电磁干扰(EMI)风险并压缩眼图张开度,使系统裕量下降、误码概率上升。

3)台阶效应:上升沿“到不了位”

在某些不匹配场景下,信号电平呈阶梯式逐步逼近目标电平。其结果是有效上升沿变缓,影响建立时间与采样窗口,对高速时序尤为不利。

TDR在排查中的角色:把“反射”映射回“结构位置”

在信号完整性测试中,时域反射计(TDR)常被用于观察传输线的阻抗分布。它通过向线路注入快速阶跃信号并分析回波,形成阻抗随时间(可对应为距离)的曲线,使工程师能够在不拆解结构的情况下识别不连续点。

为了提高判读效率,可以用波形形态与物理含义建立对应关系:

| TDR表现 | 电气含义 | 常见来源 |

|---|---|---|

| 波形向上“抬起” | 阻抗偏高(更偏感性不连续) | 线宽变窄、回流路径受阻、跨越分割平面、连接器结构过渡 |

| 波形向下“凹陷” | 阻抗偏低(更偏容性不连续) | 过孔寄生电容、焊盘过大、线宽变宽、局部介质变化 |

| 波形稳定且接近目标值 | 阻抗匹配良好 | 走线与层叠满足目标阻抗(如50Ω或100Ω差分) |

整改路径更像“闭环工程”:端接、结构与工艺缺一不可

当测试确认存在反射风险,整改通常从电路端接、结构优化与制造一致性三条路径入手:

- 端接匹配:根据拓扑与驱动能力选择源端串联、终端并联或等效端接策略,降低反射能量叠加。

- 过孔与残桩优化:通过反钻(Back-drill)、盲埋孔或优化过孔结构,减少残桩引起的反射与谐振。

- 全程阻抗控制:在PCB制造中控制介质厚度、线宽/间距与层压一致性,避免阻抗随批次漂移。

更有效的工程做法是“测试—整改—复测”的闭环:先用TDR定位结构性不连续点,再结合链路预算与系统指标验证整改是否改善眼图与误码表现。

对检测与一致性评估的意义:反射问题往往是“设计+工艺”的叠加

反射并不总是单点问题,它常由局部结构、回流路径、端接策略与制造公差共同作用。对企业而言,这意味着仅凭经验难以稳定复现结论;建立规范的测试方法学与可追溯数据证据链,才能支撑跨团队决策与供应链沟通。

在高速互连相关测试中,第三方检测的价值通常体现为测量链路的规范化与数据可比性:从阻抗板测试、TDR定位到S参数提取与系统级眼图评估,形成从“发现问题”到“验证整改”的闭环依据。

行业影响与检测支持

随着高速接口持续演进,阻抗不连续与反射引发的SI问题会更频繁地进入设计验证与量产一致性评估流程。上海德垲检测面向高速互连与PCB信号完整性需求,提供阻抗与反射相关测试支持,可覆盖PCB阻抗测试、TDR定位分析、S参数数据获取及眼图评估等环节,帮助企业更高效地识别风险点并验证整改效果。

结语

当走线成为传输线,反射就不再是“偶发波形问题”,而是高速系统必须面对的基础物理规律。理解阻抗不匹配的来源,用TDR等手段把电气现象映射到具体结构位置,并通过端接、结构与工艺三方面闭环整改,是提升高速互连稳定性与一致性的关键路径。